专业软启动器及成套控制设备生产厂家

专业软启动器及成套控制设备生产厂家

专业软启动器及成套控制设备生产厂家

专业软启动器及成套控制设备生产厂家

聚集于PCIe 3.0和4.0中的动态均衡技能,本文介绍其原理、完结及其相关的一致性测验,这种动态均衡技能被称作“Link Equalization”(链路均衡,简称为LEQ)。本系列文章分上下两篇,本文是下篇实践篇,要点介绍Rx链路均衡的测验和调试,泰克公司的主动化软件为此供给了业界最优的处理计划。

在PCIe 2.0的年代,一般只需保证了发送端的信号质量,那么整个体系也就能够正常作业;因此接纳端测验并不是必测项。但在PCIe 3.0/4.0中,由于速率成倍的添加;而且又通过长走线的传输,因此在接纳端选用了杂乱的均衡技能;因此在PCIe 3.0/4.0中接纳端测验归于必测项。

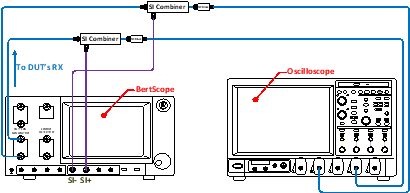

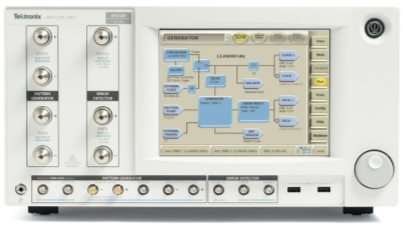

泰克公司的BSX系列的误码仪是业界高功用的串行误码仪,能够完结高达32Gbps的码型产生和误码剖析功用,一起其内部集成有预加剧模块、噪声注入、颤动注入等,支撑根据协议的握手功用。因此十分合适PCIe 3.0和4.0的接纳端测验。由于BSX系列最高支撑到32Gbps,因此它也能够充分地满意未来的PCIe 5.0的接纳端测验的要求。图1是运用BSX系列的误码仪进行PCIe 3.0d的接纳端测验的示意图。

在PCIe 3.0 & 4.0的接纳端内部集成了杂乱的单元,例如:均衡电路、时钟恢复电路、以及判定电路等;它们都是不能直接勘探到的。因此,接纳端关于测验人员来说,是一个黑盒子。PCI-SIG协会的规范开发人员,在面对此种困难时,开发了一套被称作“压力眼图(Stressed Eye)”的办法论来完结对接纳端的评价。这种办法论的中心思维便是:通过向接纳端施加一个严峻劣化的信号(即压力眼图),来检测在此种状况下,接纳端是否仍能够正确地接纳信号。因此,无论是PCIe 3.0 & 4.0 Rx LEQ的测验,基本上都能够分解成三个进程:压力眼图的校准、进入环回形式、进行误码率测验。

压力眼图的校准便是:定量地规则这个劣化信号劣化到何种程度、以及丈量该劣化信号的办法;

进入环回形式:为了检测接纳端是否正确接纳该信号;需求将现已接纳到的信号原封不动地环回到待测的发送端;然后误码仪对这个环回的信号进行判别。因此需求让待测进入环回形式;

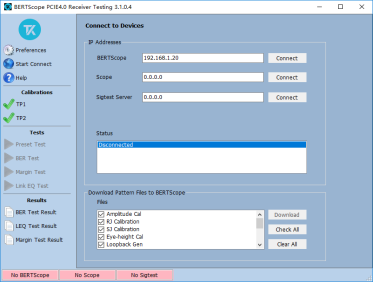

在压力眼图的校按时,涉及到信号的特性剖析以及调整迭代,这些都需求重复进行,人工手动操作十分地耗时,而且吃力不讨好。为此,泰克公司供给了业界最优的PCIe Rx主动化测验软件(BSXPCI4CEM),如图2所示。通过泰克公司的PCIe Rx主动化测验软件,能够大大缩短开发人员的研制时刻,供给产品的可靠性。

关于这个压力眼图恶劣到何种程度,必需求进行精确地定量地描绘,因此在PCIe的规范中,给出了这个压力眼图的要求。无论是PCIe 3.0仍是PCIe 4.0,校准进程都分为两个阶段:

TP1校准:TP1指的是整个参阅信道的近端,在该处校准起伏、随机颤动Rj、正弦颤动Sj、以及Tx EQ。

TP2校准:TP2指的是整个参阅信道的远端,在该处校准DMSI、CMSI、以及终究的眼高/眼宽。

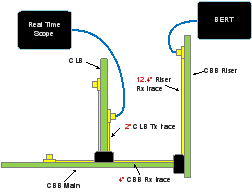

无论是PCIe 3.0,仍是PCIe 4.0,TP1的校准进程都是相同的,而且较为简略;不区别待测目标是插卡仍是体系板,整个拓扑衔接如图3所示。

TP2校原则衔接较为杂乱,耗时较长;而且关于插卡和体系板来说,拓扑衔接是不同的。而且在PCIe 3.0和PCIe 4.0中,TP2校准的战略有所不同。在PCIe 3.0中,是通过调整DMSI和Rj来到达终究的眼高/眼宽。而在PCIe 4.0中,则首要通过调整ISI来使得眼图挨近终究的眼高/眼宽,这一进程为粗调;然后再通过调整Sj、DMSI、或起伏来取得终究的眼图,这一进程为细调。

PCIe 3.0的TP2校准的拓扑衔接如图4所示。关于插卡的校准来说,在其拓扑衔接中选用的是两衔接头的拓扑结构,这是为了模仿实在的服务器背板的恶劣信道状况。整个参阅信道是由图4(a)中的物理参阅信道和SigTest通过软件嵌入的信道两部分组成。

完结了拓扑衔接之后,就能够进行PCIe 3.0的TP2的校准了。在终究眼高/眼宽的校准进程,通过调整Rj和DMSI,来到达终究的眼高/眼宽要求。这儿存在的危险是:有时分协会供给的治具一致性较差;需求很大的Rj或DMSI才干够到达终究的眼高/眼宽要求。而这并不符合在实在的状况下的Rj和DMSI的状况。

因此在PCIe 4.0中TP2的校准修改了相应的校准战略,引进了一个ISI板,优先来调理参阅信道的ISI值,来对眼图进行调整。当眼图挨近到终究的眼高/眼宽邻近时,再通过调整DMSI,Sj和起伏来到达终究的眼高/眼宽,而且DMSI,Sj和起伏的调整规模做了约束,然后能够比较实在地模仿实践中的状况。

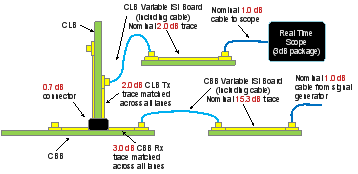

PCIe 4.0的TP2校准的拓扑衔接如图5所示。与PCIe 3.0比较,除了参阅信道的结尾嵌入了一个封装损耗之外,其他的信道都是由实在的物理信道组成的。而且由于速率翻倍,在拓扑衔接中,链路损耗的预算时必需求将衔接线缆等的损耗计入在内。值得注意的是:封装损耗是在示波器之中嵌入的,而不是在SigTest中。这个参阅封装损耗是为了模仿实在状况下的芯片封装损耗,由于RC芯片(Root Complex)的封装一般比EP芯片(Endpoint)的封装要大,因此针对RC的参阅封装损耗为5dB;而针对EP的参阅封装损耗为3dB。

如前所述,在PCIe 4.0的校准进程中,需求参阅信道的ISI值,这就涉及到一个ISI pair的迭代进程,整个迭代进程的起点是-28 dB的端到端的损耗,根据核算出来的眼高/眼宽来确认下一个ISI pair;端到端的损耗调整规模为-27 dB ~ 30dB。泰克公司的PCIe Rx主动化软件能够供给链路端到端损耗的预算,用户能够自行决定是否继续进行ISI迭代。

LEQ的测验对测验仪器提出了很高的要求。它要求测验仪器能够完结协议等级的动态应对和练习。在工业界中,一般称这样的仪器为“协议感知”型仪器(Protocol-aware Instrument)。

泰克公司的BSX系列误码仪便是这样的一种协议感知型仪器,支撑的速率最高可到32Gbps;能够支撑多种规范协议,例如PCIe 3.0 & 4.0 & 5.0、USB 3.1 & 3.2等。别的,用户还能够通过自带的Pattern Sequencer功用完结各种自主开发的规范的测验。

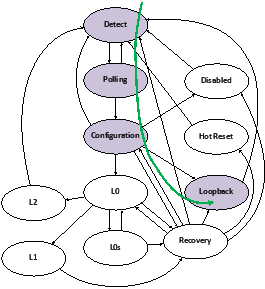

关于PCIe 3.0 & 4.0来说,从状态机的视点,有两种办法进入环回形式,如图7所示:

若成功了进入了Loopback,那么后续的误码率测验就很简略。误码仪发送Modified Compliance Pattern,查看1012个比特数据;若不超越1个误码;那么就算通过;不然就未通过。

在实践的Rx LEQ的测验中,常常由于种种原因,无法进入到环回形式;或许就算进入到了环回形式,也存在较多的误码。这个时分,咱们就需求超出一致性测验;而进行一系列的调试作业,来找出根因(Root Cause)。

泰克公司PCIe Rx主动化测验软件,除了供给协会所要求的一致性测验之外,还供给了丰厚的调试功用。再配合上BSX系列的误码仪的通用调试功用,能够为用户供给全方位的灵敏性。

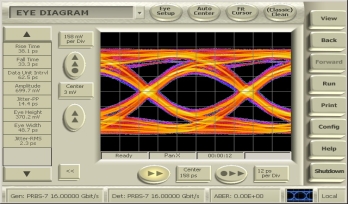

在进行Rx LEQ环回测验时,有两条数据通路:接纳数据通路和环回数据通路。由于Rx LEQ是针对接纳数据通路的测验,因此用户有必要保证不会由于环回数据通路的原因此导致误码仪的DET进行了误判。泰克的BSX系列的误码仪具有丰厚的眼图测验功用,如图8所示。这样用户再不进行任何拓扑衔接改动的状况下,就能够进行误码的调试。

用户能够运用泰克公司供给的“Empty A – Modified ComplianceB.ram”文件,就能够使得被测目标稳定地进入Compliance形式,然后通过这个ran文件进行码型切换,将被测目标的输出端切换到8Gbps或16Gbps,调查哪个预设定值能够给出最好的眼图。然后在图9中设置“Preset/Hint”成方才的预设置,就能够保证环回数据通路不会引进误判的误码。

假使排除了环回数据通路所引进的误判的误码;Rx LEQ依然存在误码。这个时分,用户需求进一步剖析误码的来历,比方说是否是DUT的均衡算法没有到达最优,然后没有像链路对端恳求最优的Tx EQ值。此刻,用户能够运用泰克公司供给的“BER Test”来对整个系数空间进行扫描,若测得的结果表明:在系数空间中存在一些系数组合能够到达没有误码,那么阐明DUT的均衡算法未到达最优。

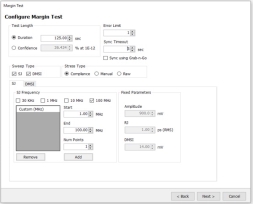

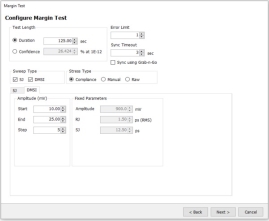

在此基础上还能够进行裕度测验。泰克的主动化软件供给对Sj和DMSI的裕度测验,如图10、11所示。

泰克公司供给了业界抢先的关于PCIe 3.0 & 4.0的一致性处理计划,通过运用泰克公司的高功用的示波器、高功用的误码仪、以及灵敏的主动化软件,能够大大缩短用户的开发时刻,使得用户的产品在市场上更具竞争力。

下一代软件界说轿车中的硬件跟着当今轿车选用更高水平的主动化(见图 1),它们集成了越来越杂乱的电子组件组合:中央处理器 (CPU)、电子操控单元 (ECU)、图形处理单元 (GPU)、新声学尺度 (NAD)、片上体系 (SoC)、传感器、加速器和存储设备。电子元件之间的架构和通讯有必要通过精心规划,以满意严厉的安全性、可靠性、功用、本钱和推迟要求。图1在车辆内,有许多ECU根据通用功用跨不同区域组合。这些区域ECU运用以太网与高功用核算渠道通讯。在核算渠道中,需求高带宽处理,以保证实时决议计划安全进行。轿车规划人员正在以与数据中心规划办法十分相似的办法运用外围组件互连快速(PCIe®)技能。将具有高速串行输出的传感器衔接到处理单元最好运用

和ASA如安在未来的软件界说车辆中结合 /

在服务器、PC等电子设备主板的出产中,往往会呈现产线的毛病,需求失效剖析工程师(FA)以及修理工程师(RMA)去快速定位出产进程傍边的毛病件,特别是一些高速信号的毛病。在整个进程中,往往需求面对许多的压力和职责,比方: 客户投诉需求及时反应 不良危险点的辨认和内部剖析 不断完善规划查看表,推动 RD 优化规划 辅导出产制程改进 团队的才干需求继续提高高速信号的特殊性可是要应对这些压力,往往也对工程师提出了很高的要求。现在来看FA/RMA工程师由于作业性质问题,要去应对上面的应战往往也很扎手,特别是高速信号相关的毛病,而且由于高速信号的特殊性,这类信号也简单出问题,其间PCIe信号是其间的典型。首要原因: 高速信号带宽高、

失效剖析利器,一学就会成为毛病定位专家 /

项目布景:项目为一个云端运算的产品,一切的高速和低速信号都要进行信号完整性测验,其间包括高速串行信号PCI-Express Gen1( 简称PCIe Gen1)。PCIe Gen1信号分为CEM和base两种状况,CEM的测验能够运用 PCI-sig协会的fixture直接进行测验;base的测验直接运用探头勘探终究端的测验点,这样就会带来一个问题,怎么才干测验到芯片的的终究端?由于,信号的互连通道不仅仅包括了PCB走线,还包括了芯片内部的布线,一般咱们以为丈量到芯片内部的Die才算终究端。该项意图PCIE 1.0是归于PCIe base的,互连CPU与以太网PHY,如下图1所示:图1 原理框图所以测验的时分,需求将probe勘探到

jitter测验问题剖析以及处理计划 /

据 Tomshardware 报导,SSD 主控大厂群联的 CEO 潘建成猜测,在未来 1 年多的时刻内,PCIe 5.0 SSD 得不到遍及,这种状况有望在 2024 下半年得到改动。上一年,AMD 在锐龙 7000 处理器的发布会上宣告 PCIe 5.0 SSD 将在 2022 年 11 月上市,但是直到本年 2 月份才有产品上市,国内电商渠道只要技嘉大雕 510K 一款类型,读速 10000 MB/s,2TB 2699 元。职业人士称,PCIe 5 SSD 的过渡比预期的要慢,可能与新技能本钱添加有关。现在,群联 PCIe 5 主控 E26 选用 12nm 技能制作,需求高规范的散热,一些PCIe 5 SSD 装备了小电扇主动散

5.0 SSD 推动缓慢,职业猜测 2024 下半年才干遍及 /

概述;CH384 是PCI-Express总线的四串口及打印口芯片,包括四个兼容16C550或许16C750 的异步串口和一个EPP/ECP 增强型双向并口,而且还能够外加CH438 芯片扩展最多达24 个串口。异步串口供给收发独立的256 字节FIFO 缓冲器,支撑IrDA红外编解码,支撑最高8Mbps的通讯波特率,能够用于PCIE 总线串口扩展、带主动硬件速率操控的PCIE 高速串口、串口组网、RS485通讯、IrDA通讯、并口/打印口扩展等。下图为其一般使用框图;特色;概述同一芯片可装备为PCIE 总线的四通道串口加并口/打印口或许四通道串口加扩展多串口。供给两线串行主机接口,能够挂接相似24C0X 的串口EEPR

总线四串口及打印口芯片 CH384 /

直播时刻:2023年3月31日(周五)下午14:00—16:10直播主题:是德科技测验丈量峰会-高速数字论坛直播简介: 国际正在变得愈加数字化、互联化和智能化,算力成为社会重要出产力之一,数据中心成为数字化转型开展的基础设备。大数据、人工智能、云核算等范畴的开展,服务器内的高速硬件数据交互需求也变得益发急迫。 作为先进的处理计划供给商,是德科技一向致力于为业界供给先进的测验、仿真和模仿计划,是德科技高速数字与光通讯测验丈量峰会将于2023年3月31日举行,峰会将约请很多业界嘉宾、媒体及生态合作伙伴,聚集新年代通讯互联技能创新,环绕新一代高速数字接口与下一代光通讯技能,评论更多落地化场景实例。扫名:

协议材料

6月6日 Microchip 有奖直播使用单片机规划安全要害型使用时应采纳的最佳实践办法

有奖直播是德科技感恩月—遇见KeysightCare - 宝贵仪器安全避坑攻略

有奖直播安森美全新 ADAS 电源 IC 提高 ADAS 体系的清晰度及安全性

具有高性价比的无线 MCU 怎么协助您将低功耗 Bluetooth®︎ 技能使用到更多产品中

中国移动携手高通及多家手机厂商完结根据IMS DC的5G新通线年十大政府职业技能趋势

欧盟计划打造自家 IRIS² 卫星互联网项目,最新预估造价 66 亿美元

日本计划拓宽本乡 Michibiki 卫星定位网络,无需再依靠美国 GPS

英飞凌收买微型机器学习范畴的领导者Imagimob,进一步增强和扩展其嵌入式AI处理计划

专为高功用存储而优化的FPGA芯片, 英特尔Agilex M 系列炽热发布!

下载泰克电源规划测验计划+图文攻略 协助工程师处理电源功率问题。有好礼

热烈庆祝坛友coyoo新书《FPGA规划实战演练》出书,参加评论即有时机赢新书!

热烈庆祝坛友coyoo新书《FPGA规划实战演练》出书,参加评论即有时机赢新书!

归纳资讯其他技能下一代网络短距离无线基站与设备RF技能光通讯规范与协议物联网与云核算有线宽带

联系人:张经理

手机:13389282290

电话:029-81616045

邮箱:13389282290@189.cn

地址:陕西自贸区西安国际港务区华南城