专业软启动器及成套控制设备生产厂家

专业软启动器及成套控制设备生产厂家

专业软启动器及成套控制设备生产厂家

专业软启动器及成套控制设备生产厂家

跟着高速数字体系的开展,高速串行数据被广泛运用,内嵌高速串行接口的FPGA也得到很多运用,相应的高速串行信号质量的测验也越来越频频和重要。一般用示波器调查信号波形、眼图、颤动来衡量信号的质量,Xilinx供给的IBERT(Integrated Bit Error Ratio Tester)作为一种高速串行信号测验的辅佐东西,使得测验更快捷,其具有不占用额定的I/O管脚和PCB空间、不破环接口信号的完整性、无搅扰、运用简略和价格低廉等特色。

IBERT是Xilinx供给用于调试FPGA芯片内高速串行接口比特误码率功用的东西,具有实时调整高速串行接口的多种参数、与体系其他模块通讯及丈量多通道误比特率等功用,支撑一切的高速串行规范,包含:PCI Express、RapidIO、千兆以太网、XAUI等。运用IBERT核测验,只需经过JTAG接口下载规划并测验硬件,无需额定的管束和接口;大幅缩减了高速串行接口测验场景的树立和调试时刻,是高速串行接口开发中抱负的调试东西。

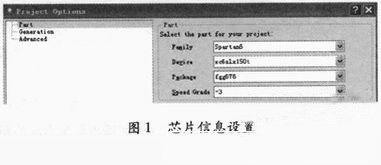

(1)翻开Core Generator12.4东西,新建规划工程,指定待测器材类型、封装、速度等级,生成工程文件。在IP Catalog窗口View by FunctionDebug&VerificationChipscope Pro下,双击IBERT,装备线速率、GTP方位和参阅时钟、体系时钟等IBERT核参数,生成可JTAG加载的bit装备文件。与生成其他核不同,IBERT核不是刺进到用户的规划中去的ngc或edn文件,而是生成本身的bit装备文件。

(2)IBERT核和ILA核(IntegratedLogicAnalyzercore),也需求连接到ICON核(Integrated Controllercore)上,但其本身具有操控、监控以及改动高速串行接口参数的逻辑,并能完结误比特功用测验。需注意的是,IBERT核只能作为一个独立的规划,不行在用户规划中例化。不同系列芯片的IBERT核在Core Generator中的装备不同。

(1)BERT(比特误码率测验)逻辑:BERT逻辑中例化了高速串行接口组件,并包含了测验形式发生器和检查器。运用Comma和Comma检测器,可供给从简略的时钟信号到彻底的PRBS形式以及成帧计数形式。可发生各种PRBS数据作为高速串行发送器的数据源,可设置多种环回,由接纳通道接纳,对高速串行接纳器的接纳数据进行相同编码的检测,核算比特误码率。

(2)DRP(动态重装备端口)逻辑:每个高速串行接口均有一个动态重装备端口,因而每个收发器特点都可在体系中改动。一切的特点和DRP地址在IBERT核中均可读可写,且可独立拜访。

(1)MGT/BERT Settings:MGT Settings部分可以设置摆幅、预加剧、均衡以及接纳采样点的方位等参数,一同可设置开环或闭环的测验办法,测验进行中可以显现线速率和所测验的高速串行接口的锁相环状况。BERT Settings部分可以设置测验发送和接纳数据的编码办法,并显现测验的误码率成果。Clock Setting部分显现收发线)DRP Settrags:可检查并设置高速串行接口的特点。

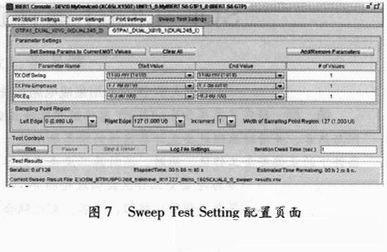

(4)Sweep Test Setting:本界面用于主动扫描测验,是IBERT供给的一项便当高效的测验办法,可设定发送和接纳的可操控参数规划,主动逐一地进行遍历性的误码测验,参数包含发送摆幅、预加剧、接纳均衡器、CDR采样数据的方位等。用户可设定每组参数重复测验次数以及测验时刻,最终点击Start即可进行扫描测验。测验数据保存在。csv文件中。只能在近端环回和远端环回测验形式中运用。

规划实例运用Xilinx公司Spatan6系列的xc6slx150t-3fgg676芯片,依据上述运用阐明,下面详细阐明运用IBERT进行测验的进程。

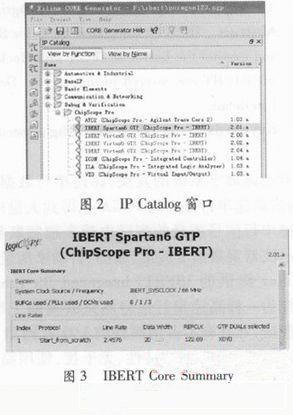

在IP Catalog窗口View by FunctionDebug&VerificationChipscope Pro下双击Ibert,如图2所示。按次序设置Ibert核线 bit,参阅时钟频率122.88 MHz,挑选被测验的GTP DUAL,设置体系时钟频率66 m、方位R7等参数,IBE RT Core Summary如图3所示,点击generate生成Ibert核的可下载bit装备文件。

首要重视PLL Status状况和Clocking Setting显现的收发时钟频率,PLL Status状况Locked标明GTP_DUAL的PLL已确认GTP的参阅时钟,GTP可正常作业。如状况是Unlocked,则要检测待测GTP的参阅时钟是否正常输入。

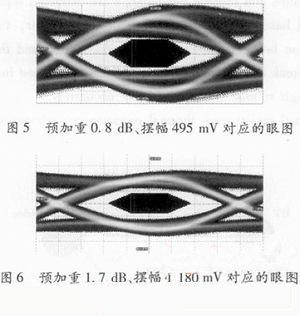

测验高速串行信号的信号质量,一般运用满意带宽和采样率的示波器测验信号眼图来评价,一但测验的眼图不契合模板要求,需求调整高速串行接口的参数。运用IBERT核可以快速完结参数修正的使命,设置Loopback Mode在开环的形式下,TX Data Pattern为PRBS7-bit,调整摆幅、预加剧参数,调查示波器上的信号眼图是否契合模板要求。图5和图6分别为调整摆幅预加剧参数前后的眼图,图5所示眼图对应预加剧0.8 dB、摆幅495 mV,眼图的眼高太小且图形磕碰模板,调整为预加剧1.7 dB、摆幅1 180 mV,眼图满意的要求如图6所示。

为确认高速串行接口的参数是否满意硬件及多种环境的需求,可经过在对端器材高速串行接口设置远端环回,设置待测验芯片的收发data pattern为一致形式,常温及高低温拷机,调查误码率是否满意要求,误码率需满意E-10.例中与图6对应的参数值条件下,对端器材高速串行接口设置远端环回误码率为4.36E-10,满意误码率要求。

Sweep Test Setting(扫描测验)其装备页面如图7所示,以Rx Sampling Point来进行误码率测验定性分析信道质量为例,较为简单了解,当同定在某个采样点进行误码测验时,误码率到达E-10时,可断定信道质量杰出。在整个UI规划内进行采样点的扫描测验时,误码率到达E-10的采样点越多,信号眼图的眼睛张得越大,间隔模板的余量越大,信道质量越好。

经过以上实例,可见IBERT具有可操作性较强的GUI图形界面,可操作性强、精确、易用,可方便地设置高速串行收发通道的各项参数,并供给了多种环回形式及多种测验鼓励源,并可经过主动扫描测验,确认收发的最佳参数。可以满意硬件测验时对高速串行收发通道信号测验的大部分需求,在毛病定位等场合均可运用。在单板的硬件测验初期,运用IBERT可以辅佐硬件测验,例如设置发送通道的各项参数,帮忙示波器丈量信号质量,而彻底不需额定的开发FPGA逻辑。进行误码率测验,作为定量丈量眼图质量、jitter等方针的弥补。从示波器看图确认出的参数并非便是最佳参数。如示波器关于均衡后的信号质量无法测验,而经过IBERT测误码率可以测验到均衡之后的节点,测验规划更大。可以预见,集成比特误码测验仪IBERT将在FPGA规划中取得广泛运用。

要害字:修改:什么鱼 引证地址:集成式比特误码率测验仪的原理、功用及在FPGA芯片调试中的运用

Socionext 供给抢先的验证服务,协助客户下降与 ASIC 和 SoC 规划流程相关的危险。在 FPGA 原型规划渠道上施行大型 SoC 规划,可以削减或许需求价值昂扬的从头规划和产品推迟的过错、缺点和毛病,在此方面咱们具有广泛而深化的专业知识。 Socionext 具有运用各种 FPGA 原型规划渠道的经历,包含 Synopsys HAPS、Protium 和 S2C。 公司是少量可以以现代规划要求所需的规划在 FPGA 渠道上施行整个 SoC 的公司之一。 在这篇博文中,咱们将讨论运用 FPGA 进行原型规划的长处,以及为什么 Socionext 可以协助您办理和下降即使是最杂乱的 ASIC 和 SoC 规划的风

经过本次协作,两边将一同创立由eFPGA赋能的Chiplet处理方案,剑指下一代芯片间互连技能的验证 硅谷圣克拉拉和德国德累斯顿,2023年5月——为了继续致力于为半导体商场供给职业抢先的处理方案,先进封装处理方案规划范畴的抢先运用研究机构Fraunhofer IIS/EAS,以及业界仅有可一同供给高端FPGA和嵌入式FPGA(eFPGA)半导体知识产权(IP)处理方案的独立供货商Achronix半导体公司(Achronix semiconductor Corporation)日前一同宣告: 两边已达成协作伙伴关系,一同构建异构chiplet处理方案,以验证其在先进的高功用体系处理方案中的功用和互操作性 。 Fraunho

我国上海——2023年4月27日——莱迪思半导体公司,低功耗可编程器材的抢先供货商,今天宣告莱迪思CrossLink-NX™ FPGA将为南京耀宇视芯科技有限公司(Metasolution)最新的增强实际(AR)和虚拟实际(VR)参阅规划供给支撑。耀宇视芯是一家抢先的同步定位和地图构建(SLAM)算法和芯片的供货商,专心于AR/VR硬件和软件处理方案,为AR/VR头显运用供给一整套六自由度(6DoF)模型。耀宇视芯总监姜爱鹏先生表明:“跟着AR/VR的新运用不断涌现,灵活性是完结其最新技能和供给沉溺式用户体会的要害。咱们很快乐可以选用莱迪思FPGA处理方案,经过其摄像头传感器桥接和SLAM算法预处理功用来加快和简化咱们的规划渠道。我

了解eFPGA IP的基础知识,它的长处,以及为什么它将成为未来先进驾驭辅佐体系(ADAS)技能的要害要素。进步轿车电气化和主动驾驭的一个首要方面是先进驾驭辅佐体系(ADAS)的遍及。现在,这些体系正敏捷运用于商场上简直一切的车辆,并且跟着技能的老练,这一趋势只会继续下去。但是,跟着技能的开展,ADAS规划人员面对的硬件应战变得越来越杂乱。在本文中,咱们将介绍ADAS的硬件需求,FPGA怎么添补这些空白,以及为什么eFPGA IP将成为下一个ADAS硬件趋势。ADAS的硬件要求ADAS在现代轿车中的开展给底层硬件带来了一些严峻的应战。在像ADAS这样的要害使命运用中,最重要的方针是保证车辆乘员的安全。这个方针要求体系精确、牢靠和实时

(eFPGA)IP是ADAS运用的抱负挑选? /

继续加强低功耗FPGA产品系列经过硬核PCIe接口将操控FPGA的优势拓宽到下一代通讯、核算和工业运用的操控功用我国上海——2023年4月20日——莱迪思半导体公司,低功耗可编程器材的抢先供货商,近来宣告推出先进的体系操控FPGA——莱迪思MachXO5T-NX™系列,旨在协助客户应对日益杂乱的体系办理规划。MachXO5T-NX FPGA是根据莱迪思Nexus™渠道的最新低功耗FPGA,具有PCIe®先进互连、更多的逻辑和存储资源以及更强壮的安全性。这些全新的低功耗器材结合了莱迪思职业抢先的低功耗、小尺度和牢靠性,旨在将莱迪思在操控FPGA范畴的长期以来的优势赋予企业网络、机器视觉和工业物联网等范畴更广泛的操控功用规划和运用中。莱

开发板根据FFMPEG的网络视频播映终端——米尔NXP I.MX 8M

ARM+FPGA开发板根据FFMPEG的网络视频播映终端——米尔NXP I.MX 8M MINI+ARTIX-7处理器开发板本篇测评由优异测评者“qinyunti”供给。01.前语米尔这款ARM+fpga开发板具有高功用的ARM MPU+多媒体才能,选用i.MX 8M Mini+Artix-7处理器,特别合适多媒体终端开发。本篇就体会建立ffmpeg开发环境,并进行功用测验,进行视频播映,演示网络视频播映器等。02.编译进程穿插编译./configure --cross-prefix=aarch64-linux-gnu- --enable-cross-compile --target-os=linux --cc=aarch64-li

规划发展、完结与展望

Verilog开发实战攻略——根据Altera EP4CE10

6月6日 Microchip 有奖直播运用单片机规划安全要害型运用时应采纳的最佳实践办法

有奖直播是德科技感恩月—遇见KeysightCare - 宝贵仪器安全避坑攻略

有奖直播安森美全新 ADAS 电源 IC 提高 ADAS 体系的清晰度及安全性

英飞凌收买微型机器学习范畴的领导者Imagimob,进一步增强和扩展其嵌入式AI处理方案

EEworld新春感恩回馈之ST新出道“高富帅”STM32F746G-DISCO 199元包邮

用心共享,一同生长!EEWORLD月月有奖优异主题/回复第28期开端啦~

安世半导体&世平集团 高效能&小型化, Nexperia MOSFET的5G处理方案 观看、下载 闯关赢好礼!

【看电源研讨会,分割3000元红包】 怎么正确完结模块化DC-DC体系规划

站点相关:信号源与示波器分析仪通讯与网络视频测验虚拟仪器高速串行测验嵌入式体系视频教程其他技能归纳资讯

联系人:张经理

手机:13389282290

电话:029-81616045

邮箱:13389282290@189.cn

地址:陕西自贸区西安国际港务区华南城